# TMC2340A Digital Synthesizer Dual 16 Bit, 50 Msps

# Features

- User-configurable phase accumulator for waveform synthesis, frequency modulation or phase modulation

- Amplitude input for amplitude modulation and gain adjustment

- Guaranteed 50 Msps pipelined data throughput rate

- 15-bit magnitude, 32-bit phase data input precision

- 16-bit offset binary or 15-bit unsigned magnitude output data format

- Input register clock enables simplify interfacing

- Low power consumption CMOS process

# Description

The TMC2340A performs waveform synthesis, modulation, and demodulation. When presented with a TTL clock signal and user-selected 15-bit amplitude and 32-bit phase increment values, the TMC2340A automatically generates quadrature matched pairs of 16-bit sine and cosine waves in DAC-compatible 16-bit offset binary format. If desired, these waveforms are easily phase or frequency-modulated on-chip, and the amplitude input facilitates gain adjustment or amplitude modulation. Digital output frequencies are restricted only by the Nyquist limit of clock rate/2, with frequency resolution of 0.012 Hz at the guaranteed maximum 50 MHz clock rate.

- Single +5V power supply

- Available in a 120-pin plastic pin grid array package (PPGA) and 120-pin metric quad flat pack (MQFP)

## **Applications**

- Digital waveform synthesis, including quadrature functions

- Digital modulation and demodulation

A new data word pair is available at the output every clock cycle. All input and output data ports are registered, with a user-configurable phase accumulator structure and input register clock enables to simplify interfacing. The phase data range over a full  $2\pi$  radians. All signals are TTL compatible.

Fabricated in a submicron CMOS process, the TMC2340A operates at the 50 MHz maximum clock rate over the full commercial temperature (0 to 70°C) and supply (4.75 to 5.25V) voltage ranges, and is available in low-cost 120 pin plastic pin grid array (PPGA) and a 120-lead metric quad flat pack (MQFP) package.

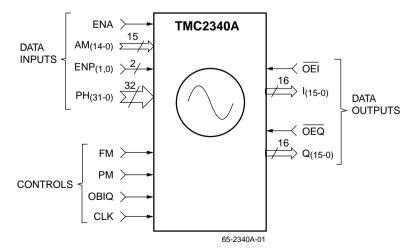

# Logic Symbol

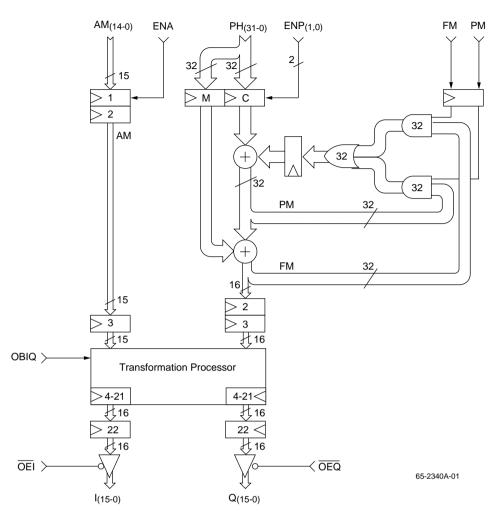

## **Block Diagram**

## **Functional Description**

#### **General Information**

The TMC2340A converts Polar (Phase and Magnitude) data into Rectangular (Cartesian) format. The first transformed result is available at the outputs 22 clock cycles after startup, with new output data available every clock cycle. All input and output data ports are registered, with input clock enables to simplify system bus connections.

The input ports accept 15-bit amplitude and 32-bit phase data, and the output ports produce 16-bit Rectangular data

words in either 16-bit offset binary or 15-bit unsigned magnitude format. The 32-bit phase accumulator handles high-accuracy (0.012Hz at the maximum clock rate) phase increment values with minimal accumulation error. The flexible input phase accumulator structure supports frequency or phase modulation, as determined by the input register clock enable ENYP1, 0 and accumulator controls FM and PM. The 16 MSBs (Most Significant Bits) of phase data are used in the transformation itself.

| Table 1. Data | Input/Output For | mats – Integer Format |

|---------------|------------------|-----------------------|

|---------------|------------------|-----------------------|

|      |      |                 | BIT#            |                 |  |  |   |                  |                  |                  |  |  |                  |      |     |

|------|------|-----------------|-----------------|-----------------|--|--|---|------------------|------------------|------------------|--|--|------------------|------|-----|

| Port | OBIQ | 31              | 30              | 29              |  |  | • | 16               | 15               | 14               |  |  | 0                | Form | nat |

| AM   | Х    |                 |                 |                 |  |  |   |                  |                  | 2 <sup>14</sup>  |  |  | 2 <sup>0</sup> . |      | U   |

| PH   | X    | ±2 <sup>0</sup> | 2 <sup>-1</sup> | 2 <sup>-2</sup> |  |  |   | 2 <sup>-15</sup> | 2 <sup>-16</sup> | 2 <sup>-17</sup> |  |  | 2 <sup>-31</sup> | (xπ) | T/U |

| 1    | 0    |                 |                 |                 |  |  |   |                  |                  | 2 <sup>14</sup>  |  |  | 2 <sup>0</sup> . |      | U   |

| 1    | 1    |                 |                 |                 |  |  |   |                  | 2 <sup>15</sup>  | 2 <sup>14</sup>  |  |  | 2 <sup>0</sup> . |      | В   |

| Q    | 0    |                 |                 |                 |  |  |   |                  |                  | 2 <sup>14</sup>  |  |  | 2 <sup>0</sup> . |      | U   |

| Q    | 1    |                 |                 |                 |  |  |   |                  | 2 <sup>15</sup>  | 2 <sup>14</sup>  |  |  | 2 <sup>0</sup> . |      | В   |

#### Notes:

- 1.  $\pm 2^0$  denotes two's complement sign or highest magnitude bit — since phase angles are modulo  $2\pi$  and phase accumulator is modulo  $2^{32}$  this bit may be regarded as  $\pm \pi$ .

- 2. All phase angles are in terms of  $\pi$  radians, hence notation "x $\pi$ ."

- 3. A sign-and-magnitude "Q" output is obtained by appending the input bit  $PH_{31}$  as a sign bit to the corresponding (i.e., delayed 22 cycles)  $Q_{14-0}$ .

- 4. A sign-and-magnitude "I" output is obtained by appending the exclusive OR of  $PH_{31}$  and  $PH_{30}$  as a sign bit to the corresponding  $I_{14-0}$ .

- When OBIQ=0, outputs I<sub>15</sub> and Q<sub>15</sub> become "do not connects" and will stay at logic HIGH. (They may be wired to V<sub>DD</sub>, left open, or connected to any logic input without damage to the part or excessive power consumption.)

- 6. Formats:

- T/U = Two's Complement/Unsigned Magnitude 32 Bits

- U = Unsigned Magnitude 15 Bits

- B = Offset Binary 16 Bits

|      | AM, I, Q |        | PH                      |                        |  |  |

|------|----------|--------|-------------------------|------------------------|--|--|

| HEX  | U        | В      | Т                       | U                      |  |  |

| FFFF |          | 32767  | -π • 2 <sup>-15</sup>   | π(2–2-15)              |  |  |

|      |          |        |                         |                        |  |  |

| 8001 |          | 1      | -π(1–2 <sup>-15</sup> ) | $\pi(1 + 2^{-15})$     |  |  |

| 8000 |          | 0      | -π                      | π                      |  |  |

| 7FFF | 32767    | -1     | π(1–2 <sup>-15</sup> )  | π(1–2 <sup>-15</sup> ) |  |  |

|      |          |        |                         |                        |  |  |

| 0001 | 1        | -32767 | π•2 <sup>-15</sup>      | $\pi \bullet 2^{-15}$  |  |  |

| 0000 | 0        | -32768 | 0                       | 0                      |  |  |

"Hex" column contains the 16 MSBs of the 32-bit phase input (16 LSBs are 0), the 15 bits of the amplitude input or the 16 bits of the offset binary output

# **Static Control Input**

OBIQ determines the numeric format of the output data: offset binary if HIGH and unsigned magnitude if LOW. This control acts with 2-cycle latency on the chip's 22-cycle data path and is normally hardwired to a system-specific state.

# **Pin Assignments**

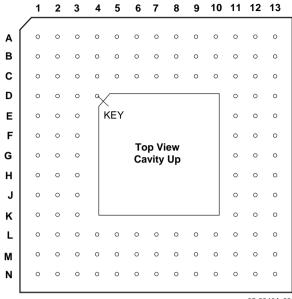

## 120-Pin Plastic Pin Grid Array (PPGA)

65-2340A-03

| Pin | Name            | Pin | Name             | Pin | Name             | Pin | Name             |

|-----|-----------------|-----|------------------|-----|------------------|-----|------------------|

| A1  | Q5              | C5  | GND              | G11 | GND              | L10 | PH <sub>31</sub> |

| A2  | Q7              | C6  | VDD              | G12 | AM <sub>12</sub> | L11 | VDD              |

| A3  | Q8              | C7  | GND              | G13 | AM <sub>13</sub> | L12 | AM <sub>3</sub>  |

| A4  | Q <sub>10</sub> | C8  | V <sub>DD</sub>  | H1  | PM               | L13 | AM <sub>4</sub>  |

| A5  | Q <sub>12</sub> | C9  | GND              | H2  | FM               | M1  | PH <sub>6</sub>  |

| A6  | Q <sub>14</sub> | C10 | GND              | H3  | V <sub>DD</sub>  | M2  | PH9              |

| A7  | Q <sub>15</sub> | C11 | V <sub>DD</sub>  | H11 | AM9              | M3  | PH <sub>11</sub> |

| A8  | I <sub>0</sub>  | C12 | I <sub>11</sub>  | H12 | AM10             | M4  | PH <sub>13</sub> |

| A9  | I2              | C13 | I <sub>13</sub>  | H13 | AM11             | M5  | PH <sub>16</sub> |

| A10 | 14              | D1  | ŌEQ              | J1  | PH <sub>0</sub>  | M6  | PH <sub>18</sub> |

| A11 | I6              | D2  | Q <sub>0</sub>   | J2  | PH <sub>1</sub>  | M7  | PH20             |

| A12 | l8              | D3  | GND              | J3  | PH <sub>3</sub>  | M8  | PH <sub>23</sub> |

| A13 | I <sub>10</sub> | D11 | GND              | J11 | GND              | M9  | PH <sub>25</sub> |

| B1  | Q3              | D12 | I14              | J12 | AM7              | M10 | PH <sub>28</sub> |

| B2  | Q4              | D13 | I15              | J13 | AM8              | M11 | ENA              |

| B3  | Q6              | E1  | GND              | K1  | PH <sub>2</sub>  | M12 | AM <sub>1</sub>  |

| B4  | Q9              | E2  | GND              | K2  | PH4              | M13 | AM <sub>2</sub>  |

| B5  | Q11             | E3  | VDD              | K3  | GND              | N1  | PH8              |

| B6  | Q13             | E11 | VDD              | K11 | GND              | N2  | PH10             |

| B7  | GND             | E12 | GND              | K12 | AM <sub>5</sub>  | N3  | PH <sub>12</sub> |

| B8  | l1              | E13 | OEI              | K13 | AM <sub>6</sub>  | N4  | PH <sub>15</sub> |

| B9  | 13              | F1  | OBIQ             | L1  | PH <sub>5</sub>  | N5  | PH17             |

| B10 | I <sub>5</sub>  | F2  | GND              | L2  | PH <sub>7</sub>  | N6  | PH <sub>19</sub> |

| B11 | 17              | F3  | CLK              | L3  | GND              | N7  | PH <sub>21</sub> |

| B12 | 19              | F11 | V <sub>DD</sub>  | L4  | V <sub>DD</sub>  | N8  | PH <sub>22</sub> |

| B13 | I <sub>12</sub> | F12 | GND              | L5  | PH <sub>14</sub> | N9  | PH <sub>24</sub> |

| C1  | Q <sub>1</sub>  | F13 | AM <sub>14</sub> | L6  | V <sub>DD</sub>  | N10 | PH <sub>26</sub> |

| C2  | Q2              | G1  | ENP <sub>1</sub> | L7  | GND              | N11 | PH <sub>29</sub> |

| C3  | V <sub>DD</sub> | G2  | ENP <sub>0</sub> | L8  | V <sub>DD</sub>  | N12 | PH <sub>30</sub> |

| C4  | GND             | G3  | GND              | L9  | PH <sub>27</sub> | N13 | AM <sub>0</sub>  |

# Pin Assignments (continued)

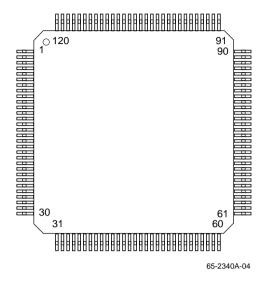

## 120-Lead Metric Quad Flat Pack (MQFP)

| Pin | Name             | Pin | Name             | Pin | Name             | Pin | Name            |

|-----|------------------|-----|------------------|-----|------------------|-----|-----------------|

| 1   | Vdd              | 31  | GND              | 61  | VDD              | 91  | VDD             |

| 2   | Q4               | 32  | PH9              | 62  | AM <sub>1</sub>  | 92  | 19              |

| 3   | Q3               | 33  | PH <sub>10</sub> | 63  | AM <sub>2</sub>  | 93  | 18              |

| 4   | GND              | 34  | V <sub>DD</sub>  | 64  | GND              | 94  | GND             |

| 5   | Q <sub>2</sub>   | 35  | PH11             | 65  | AM <sub>3</sub>  | 95  | 17              |

| 6   | Q1               | 36  | PH <sub>12</sub> | 66  | AM <sub>4</sub>  | 96  | 16              |

| 7   | Q <sub>0</sub>   | 37  | PH <sub>13</sub> | 67  | AM <sub>5</sub>  | 97  | I5              |

| 8   | V <sub>DD</sub>  | 38  | PH <sub>14</sub> | 68  | GND              | 98  | GND             |

| 9   | OEQ              | 39  | PH <sub>15</sub> | 69  | AM <sub>6</sub>  | 99  | 14              |

| 10  | GND              | 40  | PH <sub>16</sub> | 70  | AM <sub>7</sub>  | 100 | 13              |

| 11  | GND              | 41  | PH17             | 71  | AM <sub>8</sub>  | 101 | I <sub>2</sub>  |

| 12  | CLK              | 42  | V <sub>DD</sub>  | 72  | AM9              | 102 | V <sub>DD</sub> |

| 13  | GND              | 43  | PH <sub>18</sub> | 73  | AM <sub>10</sub> | 103 | l1              |

| 14  | OBIQ             | 44  | PH19             | 74  | AM <sub>11</sub> | 104 | 10              |

| 15  | ENP <sub>0</sub> | 45  | PH <sub>20</sub> | 75  | AM <sub>12</sub> | 105 | GND             |

| 16  | GND              | 46  | GND              | 76  | GND              | 106 | GND             |

| 17  | ENP1             | 47  | PH <sub>21</sub> | 77  | AM <sub>13</sub> | 107 | Q15             |

| 18  | PM               | 48  | PH <sub>22</sub> | 78  | AM <sub>14</sub> | 108 | Q14             |

| 19  | FM               | 49  | PH <sub>23</sub> | 79  | GND              | 109 | Q13             |

| 20  | VDD              | 50  | VDD              | 80  | VDD              | 110 | VDD             |

| 21  | PH <sub>0</sub>  | 51  | PH <sub>24</sub> | 81  | OEI              | 111 | Q12             |

| 22  | PH <sub>1</sub>  | 52  | PH <sub>25</sub> | 82  | GND              | 112 | Q <sub>11</sub> |

| 23  | PH <sub>2</sub>  | 53  | PH <sub>26</sub> | 83  | I <sub>15</sub>  | 113 | Q <sub>10</sub> |

| 24  | PH <sub>3</sub>  | 54  | PH <sub>27</sub> | 84  | V <sub>DD</sub>  | 114 | GND             |

| 25  | PH <sub>4</sub>  | 55  | PH <sub>28</sub> | 85  | I14              | 115 | Q9              |

| 26  | PH <sub>5</sub>  | 56  | PH <sub>29</sub> | 86  | I <sub>13</sub>  | 116 | Q <sub>8</sub>  |

| 27  | PH <sub>6</sub>  | 57  | PH30             | 87  | I <sub>12</sub>  | 117 | Q7              |

| 28  | GND              | 58  | PH <sub>31</sub> | 88  | GND              | 118 | GND             |

| 29  | PH <sub>7</sub>  | 59  | ENR              | 89  | I <sub>11</sub>  | 119 | Q <sub>6</sub>  |

| 30  | PH <sub>8</sub>  | 60  | AM <sub>0</sub>  | 90  | I <sub>10</sub>  | 120 | Q5              |

# **Pin Descriptions**

|             | Pin N                                                                                                | umber                                                                                         |                                                                                                                                                               |

|-------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name    | PPGA                                                                                                 | MQFP                                                                                          | Pin Function Description                                                                                                                                      |

| Power, Grou | and and Clock                                                                                        |                                                                                               |                                                                                                                                                               |

| VDD         | C3, E3, H3, L4,<br>L6, L8, L11, F11,<br>E11, C11, C8,<br>C6                                          | 1, 8, 20, 34, 42,<br>50, 61, 80, 84,<br>91, 102, 110                                          | The TMC2340A operates from a single +5V supply. All power and ground pins must be connected.                                                                  |

| GND         | D3, E2, E1, F2,<br>G3, K3, L3, L7,<br>K11, J11, G11,<br>F12, E12, D11,<br>C10, C9, B7, C7,<br>C5, C4 | 4, 10, 11, 13, 16,<br>28, 31, 46, 64,<br>68, 76, 79, 82,<br>88, 94, 98, 105,<br>106, 114, 118 | Ground                                                                                                                                                        |

| CLK         | F3                                                                                                   | 12                                                                                            | The TMC2340A operates from a single clock. All enabled registers are strobed on the rising edge of CLK, which is the reference for all timing specifications. |

# Pin Descriptions (continued)

|                    | Pin N                                                                                                                                                       | umber                                                            |                                                                                                                                                                                                                                                  |                                                                                                                                                                  |  |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name           | PPGA                                                                                                                                                        | MQFP                                                             | Pin Functi                                                                                                                                                                                                                                       | on Description                                                                                                                                                   |  |  |

| Inputs/Outp        | uts                                                                                                                                                         |                                                                  |                                                                                                                                                                                                                                                  |                                                                                                                                                                  |  |  |

| AM <sub>14-0</sub> | F13, G13, G12,<br>H13, H12, H11,<br>J13, J12, K13,<br>K12, L13, L12,<br>M13, M12, N13                                                                       | 78, 77, 75-69,<br>67-65, 63, 62, 60                              | $AM_{14-0}$ is the registered peak amplitude 15-bit input data port. $AM_{14}$ is the MSB.                                                                                                                                                       |                                                                                                                                                                  |  |  |

| PH <sub>31-0</sub> | L10, N12, N11,<br>M10, L9, N10,<br>M9, N9, M8, N8,<br>N7, M7, N6, M6,<br>N5, M5, N4, L5,<br>M4, N3, M3, N2,<br>M2, N1, L2, M1,<br>L1, K2, J3, K1,<br>J2, J1 | 58-51, 49-47,<br>45-43, 41-35, 33,<br>32, 30, 29, 27-21          | $PH_{31-0}$ is the registered Phase angle increment 32-bit input data port. The input phase accumulators are fed through this port in conjunction with the input enable select $ENP_{1,0}$ . $PH_{31}$ is the MSB.                               |                                                                                                                                                                  |  |  |

| I <sub>15-0</sub>  | D13, D12, C13,<br>B13, C12, A13,<br>B12, A12, B11,<br>A11, B10, A10,<br>B9, A9, B8, A8                                                                      | 83, 85, 86, 87,<br>89, 90, 92, 93,<br>95-97, 99-101,<br>103, 104 | $I_{15-0}$ is the registered X-coordinate 16-bit output data port.<br>This output is forced into the high-impedance state when<br>$\overline{OEI}$ =HIGH. I <sub>0</sub> is the LSB. I <sub>15</sub> will be "stuck at" logic HIGH if<br>OBIQ=O. |                                                                                                                                                                  |  |  |

| Q <sub>15-0</sub>  | A7, A6, B6, A5,<br>B5, A4, B4, A3,<br>A2, B3, A1, B2,<br>B1, C2, C1, D2                                                                                     | 107-109, 111-<br>113, 115-117,<br>119, 120, 122,<br>123, 125-127 | $Q_{15-0}$ is the registered Cartesian Y-coordinate 16-bit output data port. This output is forced to the high- impedance state when $\overline{OEQ}$ =HIGH. $Q_0$ is the LSB. $Q_{15}$ will remain at logic HIGH if OBIQ=0.                     |                                                                                                                                                                  |  |  |

| Controls           |                                                                                                                                                             |                                                                  |                                                                                                                                                                                                                                                  |                                                                                                                                                                  |  |  |

| ENA                | M11                                                                                                                                                         | 59                                                               | registers or                                                                                                                                                                                                                                     | nted to the input port AM are latched into the input<br>the current clock when ENA is HIGH. When ENA<br>data stored in the register remains unchanged.           |  |  |

| ENP <sub>1,0</sub> | G1, G2                                                                                                                                                      | 17, 15                                                           | phase acci                                                                                                                                                                                                                                       | presented to the PH input port is latched into the imulator input registers on the current clock, as by the control inputs ENP <sub>1, 0</sub> , as shown below: |  |  |

|                    |                                                                                                                                                             |                                                                  | ENP <sub>1,0</sub>                                                                                                                                                                                                                               | Instruction                                                                                                                                                      |  |  |

|                    |                                                                                                                                                             |                                                                  | 00                                                                                                                                                                                                                                               | No registers enabled, current data held                                                                                                                          |  |  |

|                    |                                                                                                                                                             |                                                                  | 01                                                                                                                                                                                                                                               | M register input enabled, C data held                                                                                                                            |  |  |

|                    |                                                                                                                                                             |                                                                  | 10                                                                                                                                                                                                                                               | C register input enabled, M data held                                                                                                                            |  |  |

|                    |                                                                                                                                                             |                                                                  | 11                                                                                                                                                                                                                                               | M register set to 0, C register input enabled                                                                                                                    |  |  |

|                    |                                                                                                                                                             |                                                                  |                                                                                                                                                                                                                                                  | the Carrier register and M is the Modulation<br>d 0=LOW, 1= HIGH. See the Block Diagram.                                                                         |  |  |

## Pin Descriptions (continued)

|          | Pin Nu  | umber  |                          |                                                                                                                                                                                                      |  |  |  |  |

|----------|---------|--------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name | PPGA    | MQFP   | Pin Function Description |                                                                                                                                                                                                      |  |  |  |  |

| FM, PM   | H2, H1  | 19, 18 | implemente               | etermines the internal phase Accumulator structure<br>ed on the next clock by setting the accumulator<br>d FM, PM, as shown below:                                                                   |  |  |  |  |

|          |         |        | FM, PM                   | Instruction                                                                                                                                                                                          |  |  |  |  |

|          |         |        | 00                       | No accumulation performed                                                                                                                                                                            |  |  |  |  |

|          |         |        | 01                       | PM accumulator path enabled                                                                                                                                                                          |  |  |  |  |

|          |         |        | 10                       | FM accumulator path enabled                                                                                                                                                                          |  |  |  |  |

|          |         |        | 11                       | (Nonsensical) logical OR of PM and FM                                                                                                                                                                |  |  |  |  |

|          |         |        | The accum<br>exceeded,   | DW, 1=HIGH. See the Block Diagram.<br>ulator will roll over correctly when full-scale is<br>allowing the user to perform continuous phase<br>on through $2\pi$ radians, or 360 degrees.              |  |  |  |  |

| OBIQ     | F1      | 14     | Rectangula               | select control sets the numeric format of the<br>or data: offset binary format when HIGH, and<br>when LOW. This is a static input. See the Timing                                                    |  |  |  |  |

| OEI, OEQ | E13, D1 | 81, 9  | device whe<br>LOW. Whe   | output registers are available at the outputs of the n the respective asynchronous Output Enables are n $\overline{OEI}$ or $\overline{OEQ}$ is HIGH, the respective output port ph-impedance state. |  |  |  |  |

# Absolute Maximum Ratings

(beyond which the device may be damaged)<sup>1</sup>

| Parameter                                                             | Min  | Max                       | Units |

|-----------------------------------------------------------------------|------|---------------------------|-------|

| Power Supply Voltage (VCC)                                            | -0.5 | 7                         | V     |

| Input Voltage                                                         | -0.  | 5 to (V <sub>DD</sub> +0. | 5)V   |

| Applied Voltage <sup>2</sup> Output                                   | -0.5 | VDD+0.5                   |       |

| Externally Forced Current Output                                      |      |                           |       |

| Short-circuit Duration Output (single output in HIGH state to ground) |      | 1 second                  |       |

| Operating Temperature                                                 | -20  | 110                       | °C    |

| Storage Temperature                                                   | -65  | 150                       | °C    |

| Junction Temperature                                                  |      | 140                       | °C    |

| Lead Soldering Temperature (10 sec)                                   |      | 300                       | °C    |

- 2. Applied voltage must be current limited to specified range.

- 3. Forcing voltage must be limited to specified range.

- 4. Current is specified as conventional current flowing into the device.

<sup>1.</sup> Absolute maximum ratings are limiting values applied individually while all other parameters are within specified operating conditions. Functional operation under any of these conditions is NOT implied. Performance and reliability are guaranteed only if Operating Conditions are not exceeded.

# **Operating Conditions**

| Param | eter                           | Condition  | Min  | Nom | Max  | Units |

|-------|--------------------------------|------------|------|-----|------|-------|

| Vdd   | Power Supply Voltage           |            | 4.75 | 5.0 | 5.25 | V     |

| fclk  | Clock frequency                | TMC2340A   |      |     | 20   | MHz   |

|       |                                | TMC2340A-1 |      |     | 40   | MHz   |

|       |                                | TMC2340A-2 |      |     | 50   | MHz   |

| tpwh  | Clock Pulse Width, HIGH        |            | 7    |     |      | ns    |

| tpwL  | Clock Pulse Width, LOW         |            | 6    |     |      | ns    |

| ts    | Input Data Setup Time          |            | 6    |     |      | ns    |

| tн    | Input Data Hold Time           |            | 1    |     |      | ns    |

| Vih   | Input Voltage, Logic HIGH      |            | 2.0  |     |      | V     |

| VIL   | Input Voltage, Logic LOW       |            |      |     | 0.8  | V     |

| ЮН    | Output Current, Logic HIGH     |            |      |     | -2.0 | mA    |

| IOL   | Output Current, Logic LOW      |            |      |     | 4.0  | mA    |

| TA    | Ambient Temperature, Still Air |            | 0    |     | 70   | °C    |

# **Electrical Characteristics**

| Param | eter                                        | Conditions                                                                 | Min | Nom | Max | Units |

|-------|---------------------------------------------|----------------------------------------------------------------------------|-----|-----|-----|-------|

| IDD   | Power Supply Current                        | V <sub>DD</sub> = Max, C <sub>LOAD</sub> = 25pF,<br>f <sub>CLK</sub> = Max |     |     |     |       |

|       |                                             | TMC2340A                                                                   |     |     | 140 | mA    |

|       |                                             | TMC2340A-1                                                                 |     |     | 240 | mA    |

|       |                                             | TMC2340A-2                                                                 |     |     | 290 | mA    |

| IDDU  | Power Supply Current,<br>Unloaded           | $V_{DD} = Max, \overline{OEI}, \overline{OEQ} = HIGH, f_{CLK} = Max$       |     |     |     |       |

|       |                                             | TMC2340A                                                                   |     |     | 95  | mA    |

|       |                                             | TMC2340A-1                                                                 |     |     | 175 | mA    |

|       |                                             | TMC2340A-2                                                                 |     |     | 215 | mA    |

| Iddq  | Power Supply Current,<br>Quiescent          | VDD = Max,CLK = LOW                                                        |     |     | 5   | mA    |

| CPIN  | I/O Pin Capacitance                         |                                                                            |     | 5   |     | pF    |

| Ιн    | Input Current, HIGH                         | VDD = Max, VIN = VDD                                                       |     |     | ±10 | μA    |

| lı∟   | Input Current, LOW                          | V <sub>DD</sub> = Max, V <sub>IN</sub> = 0 V                               |     |     | ±10 | μA    |

| lozн  | Hi-Z Output Leakage<br>Current, Output HIGH | VDD = Max, VIN = VDD                                                       |     |     | ±10 | μA    |

| Iozl  | Hi-Z Output Leakage<br>Current, Output LOW  | VDD = Max, VIN = 0 V                                                       |     |     | ±10 | μA    |

| los   | Short-Circuit Current                       |                                                                            | -20 |     | -80 | mA    |

| Vон   | Output Voltage, HIGH                        | IOH = Max                                                                  | 2.4 |     |     | V     |

| Vol   | Output Voltage, LOW                         | I <sub>OL</sub> = Max                                                      |     |     | 0.4 | V     |

# **Switching Characteristics**

| Parameter |                                  | Conditions <sup>1</sup> | Min | Nom | Max | Units |

|-----------|----------------------------------|-------------------------|-----|-----|-----|-------|

| tDO       | Output Delay Time                | CLOAD = 25 pF           |     |     | 16  | ns    |

| tно       | Output Hold Time                 | CLOAD = 25 pF           | 3   |     |     | ns    |

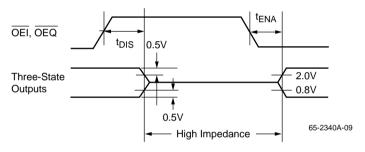

| tena      | Three-State Output Enable Delay  | CLOAD = 0 pF            |     |     | 13  | ns    |

| tDIS      | Three-State Output Disable Delay | CLOAD = 0 pF            |     |     | 13  | ns    |

Note:

1. All transitions are measured at a 1.5V level except for tENA and tDIS.

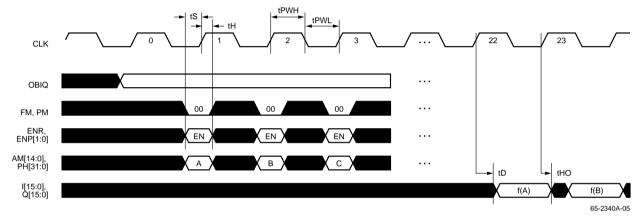

## **Timing Diagram – No Accumulation**

Note:  $\overline{OEI}$ ,  $\overline{OEQ}$  = LOW.

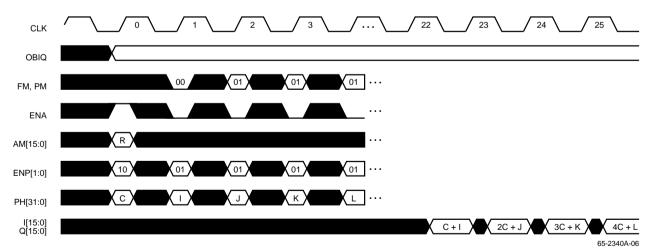

## **Timing Diagram – Phase Modulation**

- 1.  $\overline{OEI}$ ,  $\overline{OEQ}$  = LOW.

- 2. Carrier C and peak amplitude A loaded on CLK 0.

- 3. Modulation values I, J, K, L, ... loaded on CLK 1, CLK 2, etc.

- 4. Output corresponding to modulation loaded at CLK i emerged  $t_{DO}$  after CLK i +21.

- 5. To modulate amplitude, vary AM with ENA = 1.

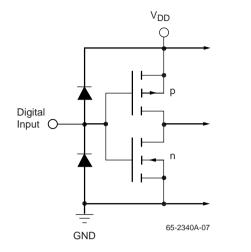

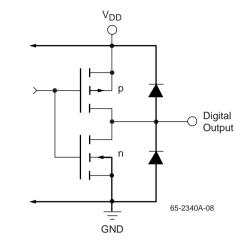

# **Equivalent Circuits and Transition Levels**

Figure 1. Equivalent Input Circuit

Figure 2. Equivalent Output Circuit

Figure 3. Transition Levels for Three-State Measurements

# **Digital Waveform Synthesis**

# Generating Unmodulated Sine and Cosine Waves

The TMC2340 can generate simultaneous quadraturematched sine and cosine waves with optional amplitude, frequency, or phase modulation. To obtain an unmodulated waveform, the user loads the desired phase step value, computed as:

$$f_{C} = \frac{2^{32} \times desired\_output\_frequency}{digital\_clock\_frequency}$$

into the 32-bit-wide carrier register via the PH input port, and applies the desired sinusoid amplitude (half of the desired peak-to-peak value) to the 15-bit-wide AM input port. As the chip's internal phase accumulator increments linearly in steps of  $f_C$ , the chip will output a series of complex number pairs representing the horizontal and vertical projections of a vector rotating about the origin, i.e., cosine and sine waves.

A procedure that will yield continuous unmodulated sinusoids is shown in Table 2.

Table 2. Generating unmodulated sinusoids

| FM | PM | ENA | AM | ENP | PH             |                                                   |

|----|----|-----|----|-----|----------------|---------------------------------------------------|

| 0  | 0  | 1   | а  | 11  | f <sub>C</sub> | loads freq & amplitude                            |

| 0  | 1  | 0   | х  | 00  | х              | starts<br>synthesizer @<br>phase = f <sub>C</sub> |

| 0  | 1  | 0   | х  | 00  | х              | continues @<br>phase = 2f <sub>C</sub>            |

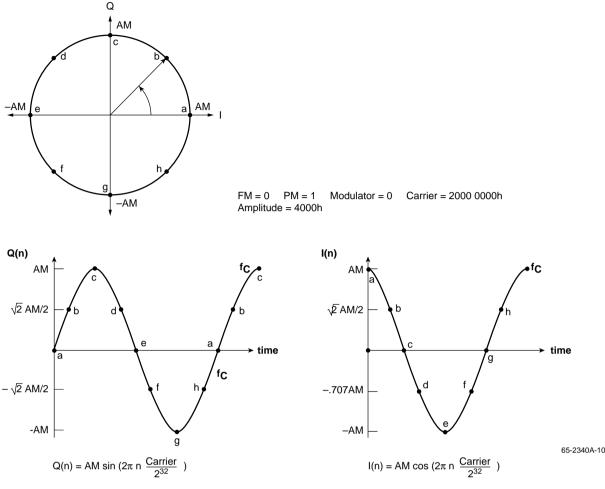

Because the chip's internal pipeline is 22 registers deep, the effects of any given set of data inputs or instructions won't be seen for 22 clock cycles. After the (22+n)th rising edge of the system clock, the outputs will be (Figure 4):

$I(22 + n) = a \cos(2\pi n f_C/2^{32})$  and

$Q(22+n) = a \sin(2\pi n f_C/2^{32}),$

where a is the (constant) amplitude and  $f_C$  is the (constant) carrier phase step or frequency ratio. For example, if we arbitrarily set a=4000h and  $f_C$ =2000 0000h, the chip will generate quadrature-matched sines and cosines at 1/8 of the

clock frequency and 1/2 of full-scale amplitude. Here, the internal phase accumulation sequence will be:

| Phase Accumulator | Phase      |

|-------------------|------------|

| 2000 0000h        | 45 degrees |

| 4000 0000h        | 90         |

| 6000 0000h        | 135        |

| 8000 0000h        | 180        |

| a000 0000h        | 225        |

| c000 0000h        | 270        |

| e000 0000h        | 315        |

| 0000 0000h        | 0          |

| 2000 0000h        | 45         |

| •••               | •••        |

On any given clock cycle, the phase angle into the chip's polar-to-rectangular converter core is that of the phase accumulator:

phase(n)=nfC

[The maximum possible output frequency is just less than half of the clock rate, per the Nyquist limit. For f>8000 0000, one obtains "negative" frequencies, because the phase increment now aliases backward. Thus, a=4000h and f=e000 0000h will generate a cosine wave and a negated sine wave at 1/8 of the clock frequency and 1/2 of full-scale amplitude.]

## **Amplitude Modulation**

By holding amplitude enable pin ENA high, the user can vary the incoming amplitude sample by sample, thereby amplitude-modulating the output signals. The output equations become:

$$I(22 + n) = a(n) x \cos (2\pi n f_C / 2^{32}) \text{ and}$$

$$Q(22 + n) = a(n) x \sin (2\pi n f_C / 2^{32}),$$

Most amplitude modulation applications employ an external adder to combine a fixed (unsigned magnitude) carrier amplitude with a sample-by-sample two's complement modulation term, such that the chip sees:

$a(n) = carrier\_amplitude + amplitude\_modulation(n)$

[Since the chip accepts only nonnegative amplitudes, this simple implementation is limited to 100% modulation, wherein the instantaneous incoming amplitude can drop to 0, but not below.]

Figure 4. Unmodulated Sinusoid Generation

Again, on any given clock cycle, the phase angle into the chip's polar-to-rectangular converter core is that of the phase accumulator:

$phase(n) = nf_{C}$

#### **Phase Modulation**

By setting ENP to 10 instead of 00 (while keeping FM = 0 and PM = 1), the user can load a new modulating phase shift into the PH port on each clock cycle. If we label this modulating term p(n), the output equations become:

$I(n+22) = a(n) x \cos(2\pi(p(n)+nf_{C})/2^{32})$

$Q(n+22) = a(n) x sin(2\pi(p(n)+nf_C)/2^{32})$

Figure 5 depicts the internal subsarrier architecture in this mode. If we again load carrier =  $2000\ 0000$ h, but now alternately apply phase modulation (p) terms 0 and  $1000\ 000$ h, the internal phase sequence will be:

| Phase Modulation | Phase                                      |

|------------------|--------------------------------------------|

| 2000 0000h       | normal unmodulated start                   |

| 5000 0000h       | phase advanced by an additional 1000 0000h |

| 6000 0000h       | phase back to normal<br>progression        |

| 9000 0000h       | phase advanced by an additional 1000 0000h |

| a000 0000h       | phase back to normal<br>progression        |

| d000 0000h       | phase advanced by an additional 1000 0000h |

| e000 0000h       | phase back to normal<br>progression        |

Here, on any given clock cycle, the phase angle into the chip's polar-to-rectangular converter core is that of the phase accumulator, plus the current value of the modulator:

phase(n) = nfC + p(n)

## **Frequency Modulation**

By setting ENP = 10, FM = 1, and PM = 0, the user can load a new frequency modulation sample into the PH port on each clock cycle. In phase modulation, the angular modulation term was outside of the phase accumulator/integration loop. Therefore, each modulation sample affected only a single complex output sample. In frequency modulation, since the angular modulation occurs within the phase accumulator, each modulation sample affects all future outputs. Figure 5 depicts the phase accumulator architecture in this mode.

Consider the following phase advance sequence, using the same 2000 0000h carrier and alternate 0 and 1000 000h modulation, this time in frequency modulation instead of phase modulation mode:

| Phase Accumulator | Phase                                     |

|-------------------|-------------------------------------------|

| 2000 0000h        | unmodulated                               |

| 5000 0000h        | phase advanced by 10000000+20000000       |

| 7000 0000h        | unmodulated—phase<br>advanced by 20000000 |

| a000 0000h        | phase again advanced by 30000000          |

| c000 0000h        | advance by 20000000                       |

| f000 0000h        | advance by 30000000                       |

Here, on any given clock cycle, the phase angle into the chip's polar-to-rectangular converter core is that of the previous cycle, plus carrier + modulator:

phase(n+1) = phase(n) + fC + p(n)

and is the same as the present value in phase accumulator. In frequency modulation mode, introducing a single nonzero modulation term will shift the phases of all outputs which follow. In contrast, in phase modulation, introducing a single nonzero modulation term will shift the phase of only one output.

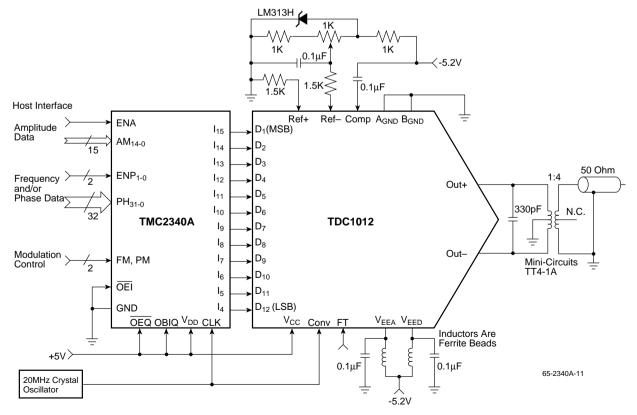

# Digital Synthesizer with the TDC1012 D/A Converter

The TDC1012 is an ideal D/A converter for digital synthesis, exhibiting a Spurious-Free Dynamic Range of greater than 70dB. Connection between the TMC2340A and TDC1012 is straightforward, as illustrated in Figure 5.

Either the I or the Q output of the TMC2340 may be connected to the D/A; two converters are used for quadrature synthesis. The trans-former-coupled output circuit shown is recommended for minimum distortion. See the TDC1012 datasheet for details.

Figure 5. Frequency Synthesizer

The TMC2340A needs to be initialized to tell it what frequency and amplitude sinusoid to generate. To initialize amplitude, apply the desired full-scale amplitude to the AM input port of the TMC2340A (AM14 through AM0) and pull ENA HIGH for one clock cycle. This will load the amplitude. If ENA is held HIGH, then the amplitude will follow the inputs on the AM port. If the user assumes an implied binary point before the MSB of the AM port, the input range will be 0 to just under 1, and the outputs will fall between 0 and 2, with binary points after I15 and Q15.

To set the frequency, the C register must be loaded with a value which is the phase increment per clock cycle. If the binary point is considered to be just left of the MSB (input range is 0 to almost 1) then the output frequency is the TMC2340A clock frequency multiplied by the number loaded into C. Since C is 32 bits wide, with a 20MHz clock, one LSB represents a frequency increment of 0.005Hz.

To load the C register, set  $ENYP_1=1$  and  $ENYP_0=0$ ; the data presented at the PH port will be loaded on the next clock rising edge.

At this point the TMC2340A has been initialized and can be put into one of three modes depending upon the states of FM and PM:

Mode 0 FM = 0, PM = 0In this mode the chip is in standby. The unchanging output corresponds to AM cos(PM) on the I outputs with PM being the phase increment.

Mode 1 FM=1, PM=0

Frequency Modulation Mode. The chip generates an output signal of peak amplitude AM and frequency determined by accumulating the sum of the phase increment values in the C and M registers (more about the M register in a later section).

Mode 2 FM=0, PM=1

Phase Modulation Mode. The TMC2340A generates a sinusoid of the frequency represen-ted in the C register and the peak amplitude in the AM register. On each clock cycle, the phase of the signal is offset by the value in the M register. Use this mode with ENP=00 for unmodulated sinewave synthesis.

#### Modulation

The output of the TMC2340A can be phase (Mode 2) or frequency (Mode 1) modulated. An unmodulated sinusoid results if the contents of registers C and M are held constant. Its frequency is set by C (Mode 2) or C+ M (Mode 1). Since the state of the M register is not defined at power up, the M register should be loaded or cleared to begin operation.

If the signal is to be frequency modulated then the modulation signal is loaded into the M register. The format for the frequency is the same as that for the C register.

If ENYP1, 0 = 0, 1 then the data value present at the PH port is automatically loaded on each clock rising edge.

For phase modulation, the phase deviation is loaded into the M register (same manner as for frequency modulation). The units of the phase offset are cycles and full-scale is just under one output cycle per TMC2340A clock cycle. The MSB represents a phase of 180°, and the LSB a phase of about  $8 \times 10^{-8}$  degrees (eight one-hundred millionths of a degree) or  $\pi/2^{31}$  radians.

To synchronize two TMC2340As, first load them with their respective data in mode 0, then switch them simultaneously to either Mode 1 or Mode 2.

# Calculating Frequency, Amplitude, and Phase Input Values for the TMC2340A

This Application Brief discusses equations which simplify the calculation of register values which control the TMC2340A. These values allow the generation of output carrier frequency, frequency or phase modulation, and output amplitude.

The results of the equations are converted to binary register values and should be rounded to the resolution of the applicable register (32 or 15-bits). For negative values of phase or frequency modulation, use these equations for positive values and see Table 1 to convert them to negative values.

The TMC2340A operates by continuously incrementing a register (phase accumulator) that rolls over when it becomes full. For example, if the next increment to the phase accumulator causes it to overflow by 47 LSBs, the phase accumulator retains the value 47. The value present in the carrier register (C) is the amount by which the phase accumulator is incremented each system clock cycle. As the value of the carrier register is increased, the value with which the phase accumulator is increased, resulting in an increased carrier frequency.

The magnitude of the carrier is determined or modulated by the value loaded In the AM register. Phase modulation is accomplished by adding the value of the phase accumulator to the value of the modulation (M) register. This adds an offset to the phase of the carrier. This does not affect the increment value of the phase accumulator and therefore affects only the phase of the carrier, leaving the frequency constant.

Adding the value of the modulation register to the phase accumulator along with the value of the carrier register on each clock cycle results in a shift in frequency. This is because the phase accumulator is incremented by a different amount each clock cycle.

Frequency or phase modulation is selected with the FM and PM input pins which configure the TMC2340A. The equations presented herein are useful for setting carrier frequency

and phase, output amplitude, and frequency and phase modulation. To modulate the carrier with an external signal, the signal must be digitized and those values loaded into the modulation inputs of the TMC2340A. The carrier and modulation registers are loaded through the  $PH_{31-0}$  inputs. The  $ENP_{1,0}$  inputs select the desired register. The amplitude register is loaded through the  $AM_{14-0}$  inputs.

#### **CARRIER FREQUENCY:**

Carrier Register (C) Value =  $\frac{\text{Desired Carrier Frequency}}{\text{Clock Frequency}} \times 2^{32}$

#### AMPLITUDE AND AMPLITUDE MODULATION:

AM Register Value =  $\frac{\text{Desired Output Amplitude}}{\text{Full-Scale Output Amplitude}} \times (2^{15} - 1)$

#### FREQUENCY MODULATION:

Modulation Register (M) Value =  $\frac{\text{Desired Change in Carrier Frequency}}{\text{Clock Frequency}} \times 2^{32}$

#### PHASE-MODULATION:

Modulation Register (M) Value =  $\frac{\text{Desired Change in Phase in Radians (Degrees)}}{2\pi(360^\circ)} \times 2^{32}$

#### EXAMPLE 1: Set carrier frequency to 3.579545 MHz with a system clock of 20MHz.

Carrier Register (C) Value =  $\frac{\text{Desired Carrier Frequency}}{\text{Clock Frequency}} \times 2^{32} = \frac{3.579545 \times 10^6}{20 \times 10^6} \times 2^{32}$

#### EXAMPLE 2: Set output amplitude to be 12.2% of full-scale.

AM Register Value =  $\frac{\text{Desired Output Amplitude}}{\text{Full-Scale Output Amplitude}} \times (2^{15} - 1) = \frac{12.2}{100.0} \times 32767$

AM = 3,998 = 0F9Eh = 0001 1111 0011 1100 = AM14-0

#### EXAMPLE 3: Change carrier frequency by 10kHz with a system clock of 3 MHz.

Modulation Register (M) Value =  $\frac{\text{Desired Change in Carrier Frequency}}{\text{Clock Frequency}} \times 2^{32}$

$$M = \frac{10 \times 10^3}{3 \times 10^6} \times 2^{32} = 14,316,558 = 00DA 740Eh$$

$M = 0000\ 0000\ 1101\ 1010\ 0111\ 0100\ 0000\ 1110 = PH_{31-0}$

#### EXAMPLE 4: Advance the phase of any carrier frequency by 12°.

Modulation Register (M) Value =  $\frac{\text{Desired Change in Phase}}{360^{\circ}} \times 2^{32} = \frac{12}{360} \times 2^{32}$

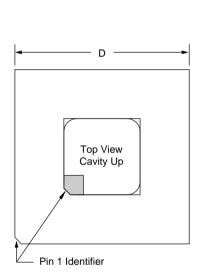

## **Mechanical Dimensions**

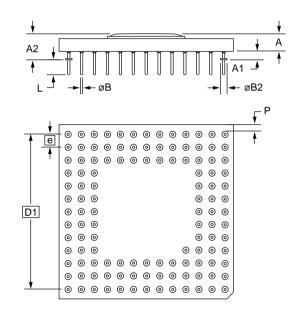

### 121-Pin PPGA Package

| Symbol | Inc       | hes   | Millim    | Notes |       |  |

|--------|-----------|-------|-----------|-------|-------|--|

| Symbol | Min.      | Max.  | Min.      | Max.  | Notes |  |

| А      | .080      | .160  | 2.03      | 4.06  |       |  |

| A1     | .040      | .060  | 1.01      | 1.53  |       |  |

| A2     | .125      | .215  | 3.17      | 5.46  |       |  |

| øB     | .016 .020 |       | 0.40      | 0.51  | 2     |  |

| øB2    | .050      | NOM.  | 1.27      | 2     |       |  |

| D      | 1.340     | 1.380 | 33.27     | 35.05 | SQ    |  |

| D1     | 1.200 BSC |       | 30.48 BSC |       |       |  |

| е      | .100 BSC  |       | 2.54 BSC  |       |       |  |

| L      | .110      | .145  | 2.79      | 3.68  |       |  |

| L1     | .170      | .190  | 4.31      | 4.83  |       |  |

| М      | 1         | 3     | 13        |       | 3     |  |

| Ν      | 120       |       | 120       |       | 4     |  |

| Р      | .003 —    |       | .076      | _     |       |  |

#### Notes:

- 1. Pin #1 identifier shall be within shaded area shown.

- 2. Pin diameter excludes solder dip finish.

- 3. Dimension "M" defines matrix size.

- 4. Dimension "N" defines the maximum possible number of pins.

- 5. Orientation pin is at supplier's option.

- 6. Controlling dimension: inch.

18

# Mechanical Dimensions (continued)

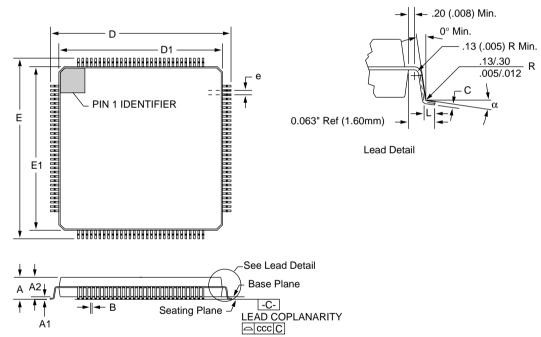

## 120-Lead MQFP Package

| Symbol | Inc       | hes        | Millim  | Notes      |       |  |

|--------|-----------|------------|---------|------------|-------|--|

| Symbol | Min. Max. |            | Min.    | Max.       | NOLES |  |

| Α      | _         | .154       | _       | 3.92       |       |  |

| A1     | .010      | _          | .25     | —          |       |  |

| A2     | .125      | .144       | 3.17    | 3.67       |       |  |

| В      | .012      | .018       | .30     | .45        | 3, 5  |  |

| С      | .005      | .009       | .13     | .23        | 5     |  |

| D/E    | 1.219     | 1.238      | 30.95   | 31.45      |       |  |

| D1/E1  | 1.098     | 1.106      | 27.90   | 28.10      |       |  |

| е      | .0315 BSC |            | .80 BSC |            |       |  |

| L      | .026      | .037       | .65     | .95        | 4     |  |

| Ν      | 12        | 20         | 120     |            |       |  |

| ND     | 3         | 0          | 3       |            |       |  |

| α      | 0°        | <b>7</b> ° | 0°      | <b>7</b> ° |       |  |

| CCC    | — .004    |            | —       | .10        |       |  |

- 1. All dimensions and tolerances conform to ANSI Y14.5M-1982.

- 2. Controlling dimension is millimeters.

- 3. Dimension "B" does not include dambar protrusion. Allowable dambar protrusion shall be .08mm (.003in.) maximum in excess of the "B" dimension. Dambar cannot be located on the lower radius or the foot.

- 4. "L" is the length of terminal for soldering to a substrate.

- 5. "B" & "C" includes lead finish thickness.

## **Ordering Information**

| Product Number | Temperature<br>Range | Speed<br>Grade | Screening  | Package                        | Package<br>Marking |

|----------------|----------------------|----------------|------------|--------------------------------|--------------------|

| TMC2340AH5C    | 0° to 70°C           | 20 MHz         | Commercial | 121-Pin Plastic Pin Grid Array | 2340AH5C           |

| TMC2340AH5C1   | 0° to 70°C           | 40 MHz         | Commercial | 121-Pin Plastic Pin Grid Array | 2340AH5C1          |

| TMC2340AH5C2   | 0° to 70°C           | 50 MHz         | Commercial | 121-Pin Plastic Pin Grid Array | 2340AH5C2          |

| TMC2340AKEC    | 0° to 70°C           | 20 MHz         | Commercial | 120-Pin Metric Quad FlatPack   | 2340AKEC           |

| TMC2340AKEC1   | 0° to 70°C           | 40 MHz         | Commercial | 120-Pin Metric Quad FlatPack   | 2340AKEC1          |

| TMC2340AKEC2   | 0° to 70°C           | 50 MHz         | Commercial | 120-Pin Metric Quad FlatPack   | 2340AKEC2          |

The information contained in this data sheet has been carefully compiled; however, it shall not by implication or otherwise become part of the terms and conditions of any subsequent sale. Raytheon's liability shall be determined solely by its standard terms and conditions of sale. No representation as to application or use or that the circuits are either licensed or free from patent infringement is intended or implied. Raytheon reserves the right to change the circuitry and any other data at any time without notice and assumes no liability for errors.

#### LIFE SUPPORT POLICY:

Raytheon's products are not designed for use in life support applications, wherein a failure or malfunction of the component can reasonably be expected to result in personal injury. The user of Raytheon components in life support applications assumes all risk of such use and indemnifies Raytheon Company against all damages.

Raytheon Electronics Semiconductor Division 5580 Morehouse Drive San Diego, CA 92121 619 457 1000 800 722 7074 Fax 619 455 6314 applications@lj.sd.ray.com